이미지: CRC-32 알고리즘 개요 다이어그램

게시됨: 2026년 1월 12일 오전 9시 14분 50초 UTC

마지막으로 업데이트되었습니다: 2026년 1월 9일 오후 10시 7분 41초 UTC

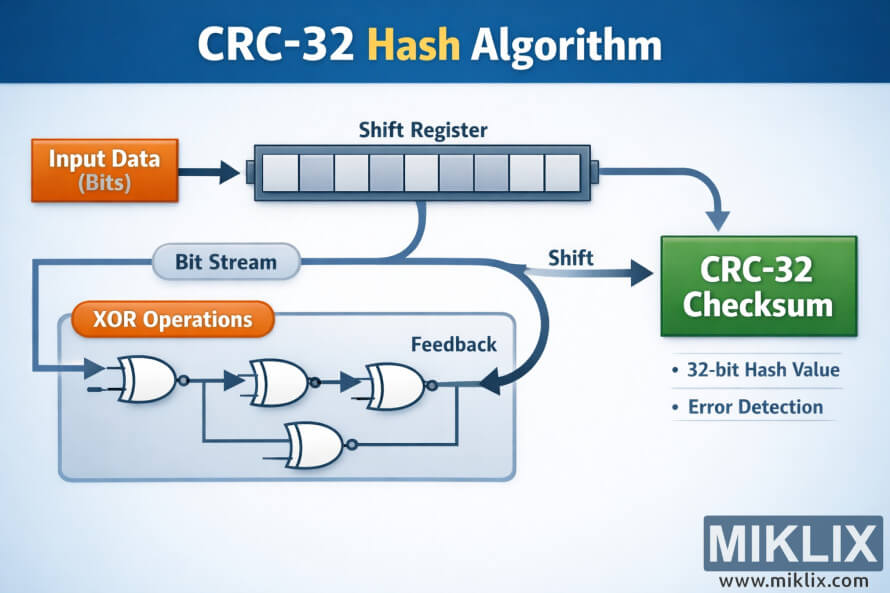

CRC-32 해시 알고리즘의 교육용 시각화 자료로, 입력 비트가 XOR 피드백이 있는 시프트 레지스터를 통해 흐르면서 체크섬을 생성하는 과정을 보여줍니다.

CRC-32 Algorithm Overview Diagram

이 이미지의 사용 가능한 버전

아래에서 다운로드할 수 있는 이미지 파일은 이 웹사이트의 기사 및 페이지에 삽입된 이미지보다 압축률이 낮고 해상도가 높으며, 대역폭 소비를 줄이기 위해 파일 크기에 더 최적화되어 있어 품질이 더 높습니다.

일반 사이즈 (1,536 x 1,024)

대형 사이즈 (3,072 x 2,048)

매우 큰 크기 (4,608 x 3,072)

초대형 사이즈 (6,144 x 4,096)

코믹하게 큰 사이즈 (1,048,576 x 699,051)

- 아직 업로드 중... ;-)

이미지 설명

이 이미지는 "CRC-32 해시 알고리즘"이라는 제목의 가로 방향 교육용 도표로, 깔끔하고 밝은 배경에 파란색 그라데이션 헤더가 있습니다. 주요 흐름은 왼쪽에서 오른쪽으로 진행되어 처리 과정의 연속적인 특성을 강조합니다. 맨 왼쪽에는 "입력 데이터(비트)"라고 표시된 주황색 직사각형 상자가 있는데, 이는 들어오는 이진 데이터 스트림을 나타냅니다. 이 상자에서 굵은 화살표가 위쪽 중앙에 있는 "시프트 레지스터"라고 표시된 긴 가로 블록을 가리킵니다. 시프트 레지스터는 작은 셀들이 나란히 배열된 형태로 표현되어 데이터 비트가 한 번에 모두 이동하는 것이 아니라 레지스터를 통해 단계적으로 이동함을 보여줍니다.

시프트 레지스터 오른쪽에서 곡선 화살표가 아래쪽과 오른쪽으로 휘어져 "CRC-32 체크섬"이라고 표시된 큰 녹색 상자를 가리킵니다. 이 마지막 상자는 처리 과정의 최종 결과를 시각적으로 강조한 것입니다. 녹색 상자 아래에는 결과를 간략하게 요약한 두 개의 항목이 있습니다. 하나는 결과가 32비트 해시 값임을 나타내고, 다른 하나는 이 값이 오류 감지에 사용된다는 것을 설명합니다.

시프트 레지스터 아래에는 데이터 처리 과정에서 피드백과 비트 단위 논리가 레지스터에 어떤 영향을 미치는지 시각적으로 보여주는 보조 경로가 있습니다. "비트 스트림"이라고 표시된 둥근 연한 파란색 캡슐이 가로로 뻗어 있는데, 이는 레지스터에서 나가는 비트들이 연속적인 흐름으로 처리됨을 나타냅니다. 이 흐름에서 경로가 이어져 "XOR 연산"이라고 표시된 크고 반투명한 파란색 패널이 나타납니다. 이 패널 안에는 화살표로 연결된 여러 개의 양식화된 논리 게이트 기호가 있습니다. 이 게이트들은 배타적 논리합(XOR) 연산의 동작을 기술적인 정확성보다는 단순한 아이콘 스타일로 표현한 것입니다.

XOR 패널 내에서 화살표는 게이트들을 순차적으로 연결하여 비트들이 결합된 후 여러 단계의 논리적 혼합을 거치는 과정을 보여줍니다. "피드백"이라고 표시된 눈에 띄는 화살표는 XOR 블록의 오른쪽에서 시프트 레지스터 쪽으로 다시 올라가며, 처리된 데이터의 일부가 레지스터로 되돌아가는 것을 나타냅니다. 이 고리 모양의 화살표는 더 두껍고 진하게 표시되어 정확한 다항식이나 구현 세부 사항을 명시하지 않고도 피드백의 개념을 시각적으로 명확하게 전달합니다.

아래쪽 경로에서 "시프트"라고 표시된 또 다른 화살표가 갈라져 나와 녹색 "CRC-32 체크섬" 상자를 가리키며, 반복적인 시프트와 피드백을 거쳐 누적된 결과가 체크섬으로 나타난다는 것을 강조합니다. 전체적인 색상 구성은 입력은 주황색, 처리 및 논리는 파란색, 출력은 녹색을 사용하여 사용자가 각 단계를 빠르게 구분할 수 있도록 합니다. 이 레이아웃은 저수준의 기술적 세부 사항을 피하고 대신 고수준 개념, 즉 비트가 입력되어 시프트 레지스터를 통과하고 피드백 루프에서 XOR 논리와 결합된 후 최종적으로 오류 감지에 사용되는 CRC-32 체크섬을 생성하는 과정을 전달하는 데 중점을 둡니다.

이 이미지는 다음과 관련이 있습니다: CRC-32 해시 코드 계산기